Difference between revisions of "IONI connector pinout"

From Granite Devices Knowledge Wiki

| [checked revision] | [checked revision] |

(→Pinout) |

(→Pinout) |

||

| Line 73: | Line 73: | ||

Note 1: pins marked as ''Not connected'' are left empty for to make larger clearance for high voltage signals. Leave these pins unconnected on motherboard designs. | Note 1: pins marked as ''Not connected'' are left empty for to make larger clearance for high voltage signals. Leave these pins unconnected on motherboard designs. | ||

| − | Note 2: Each power signal is present in two pin groups (internally parallel) and these signals should be wired parallel on motherboard | + | Note 2: Each power signal is present in two pin groups (internally parallel) and these signals should be wired parallel on motherboard. |

==Electrical ratings== | ==Electrical ratings== | ||

Revision as of 15:19, 6 February 2015

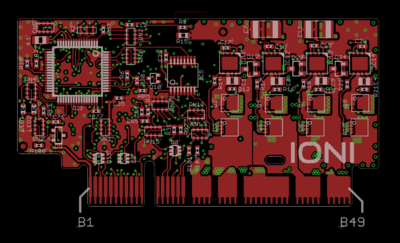

IONI card edge connector fits into a standard PCI-Express 8X socket connector.

Pinout

The pinout of IONI drive is provided in the following table.

- I/O and low voltage signals

| Pin | Signal name | Pin | Signal name | |

|---|---|---|---|---|

| A1 | GND | B1 | 5V_IN | |

| A2 | RS485_A | B2 | RS485_B | |

| A3 | ADDRSEL1 | B3 | ADDRSEL2 | |

| A4 | HSIN1 | B4 | HSIN2 | |

| A5 | ANAIN- | B5 | ANAIN+ | |

| A6 | GPI1 | B6 | GPI2 | |

| A7 | GPI3 | B7 | GPI4 | |

| A8 | GPO1 | B8 | GPO2 | |

| A9 | GPO3 | B9 | GPO4 | |

| A10 | GPO5 | B10 | GPO6 | |

| A11 | REGEN_OUT | B11 | MECH_BRAKE_OUT | |

| A12 | ENABLE_IN | B12 | Reserved/NC | |

| A13 | STO2 | B13 | HALL_W | |

| A14 | HALL_V | B14 | HALL_U | |

| A15 | CHA- | B15 | CHA+ | |

| A16 | CHB- | B16 | CHB- | |

| A17 | CHC- | B17 | CHC- |

- Power signals

| Pin | Signal name | Pin | Signal name | |

|---|---|---|---|---|

| A18-A22 | GND | B18 | Not connected | |

| A23 | Not connected | B19-B22 | HV+ | |

| A24-A27 | PHASE1 | B23 | Not connected | |

| A28 | Not connected | B24-B27 | PHASE2 | |

| A29-A37 | PHASE3 | B28 | Not connected | |

| A38 | Not connected | B29-B37 | PHASE4 | |

| A39-A43 | PHASE1 | B38 | Not connected | |

| A44 | Not connected | B39-B43 | PHASE2 | |

| A45-A49 | GND | B44 | Not connected | |

| B45-B49 | HV+ |

Note 1: pins marked as Not connected are left empty for to make larger clearance for high voltage signals. Leave these pins unconnected on motherboard designs.

Note 2: Each power signal is present in two pin groups (internally parallel) and these signals should be wired parallel on motherboard.

Electrical ratings

| Signal names | Allowed input voltages/output voltage | Internal input/output impedance (Ω) | Internal pull impedance (Ω) |

|---|---|---|---|

| 5V_IN | 5V +/-10% | - | - |

| HV+ | 0 – 55 V | - | - |

| RS485_A/B | RS485 serial bus, 2.7-5.5V signal level | >10k | - |

| ADDRSEL1, ADDRSEL2 | External address setting pull-down resistors to ground (minimum 2.2 kΩ). See article Setting IONI bus address. | - | 2.2k pull-up |

| HSIN1, HSIN2 | Logic low -0.3-1.0V, logic high 2.7-5.5V | - | 2.2k pull-up |

| ANAIN-, ANAIN+ | +/- 11V | 8k | - |

| GPI1...GPI4 | Logic low -0.3-1.0V, logic high 2.7-5.5V | - | 2.2k pull-up |

| GPO1...GPO6 | Logic low 0V, logic high 3.3V | 220 | - |

| MECH_BRAKE_OUT | Logic low 0V, logic high 3.3V | 220 | - |

| REGEN_OUT | Logic low 0V, logic high 3.3V | 220 | - |

| ENABLE_IN | Logic low -0.3-1.0V, logic high 2.7-26V | 5k | 10k pull-down |

| STO2 | Logic low -0.3-2.0V, logic high 4.5-26V | 8k | 20k pull-down |

| HALL_U/V/W | Logic low -0.3-1.0V, logic high 2.7-5.5V | - | 2.2k |

| CHA/B/C+ | RS422 receiver, 2.7-5.5V signal level | - | 2.2k |

| CHA/B/C- | RS422 receiver, 2.7-5.5V signal level | - | 1.1k pull to 2.5V |